计算机组成与体系结构

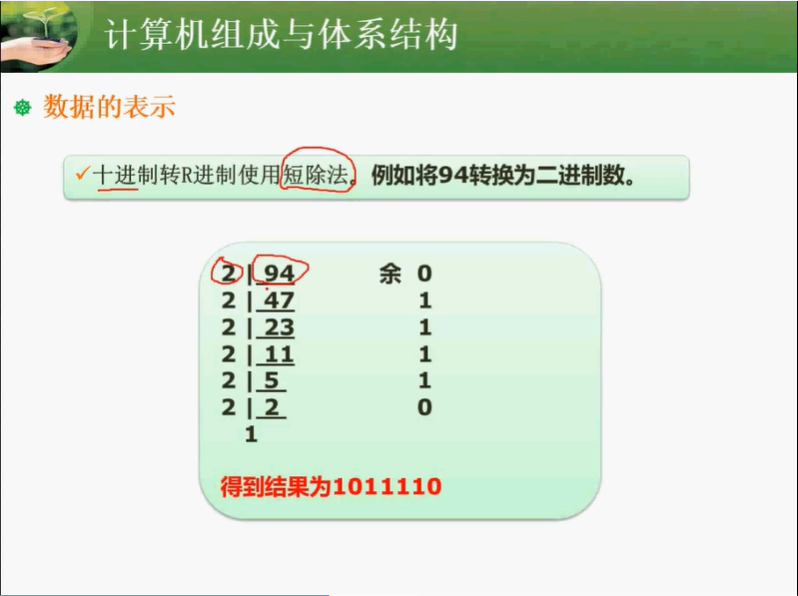

数据的表示(进制转换)

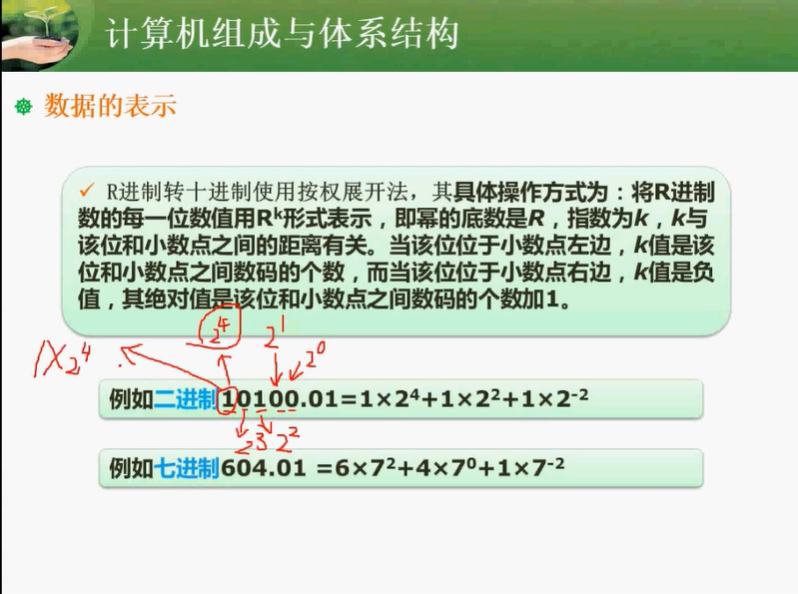

R进制转十进制使用按权展开法:

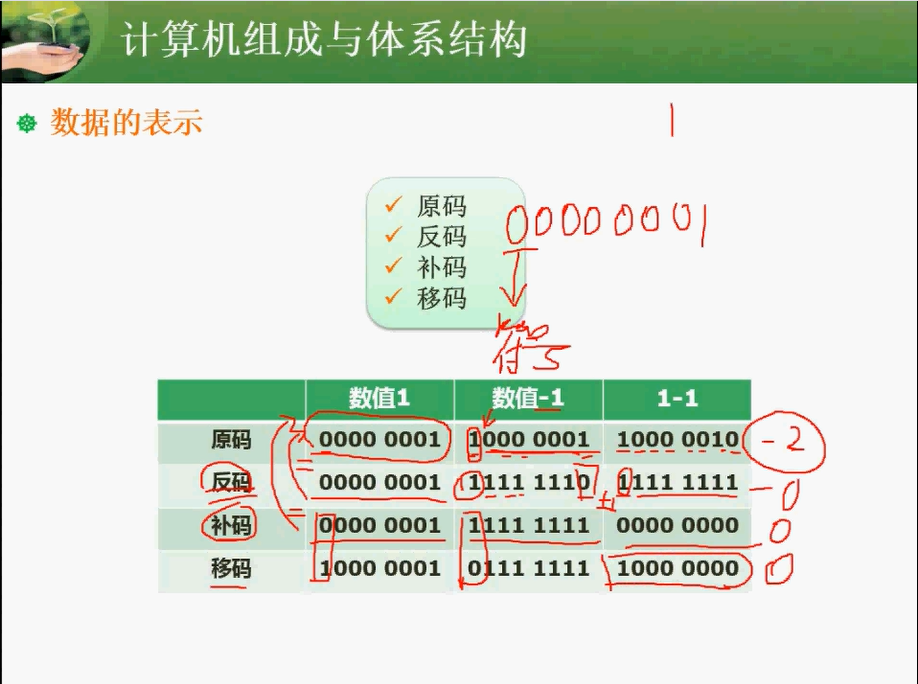

源码,反码,补码,移码

第一位是符号位,1表示负数,0表示正数

原码: 就是将数转成二进制,填满一个字节数(一般是8位 1byte = 8bit),首位是符号位。0有两种写法,0000 0000(+0) 和 1000 0000 (-0), 1-1不等于0,而是-2, 所以不能用于机器运算。

反码: 正数不变,负数是原码的取反。0有两种表示方法,0000 0000(+0)和1111 1111(-0)。 1-1等于-0

补码: 正数不变, 负数是反码 + 1。0只有一种表示方法,0000 0000 。1-1=0, 符合运算规则

移码:正数和负数的符号位调换,1表示正数,0表示负数。其他和补码一致。通常用于浮点运算的阶码。

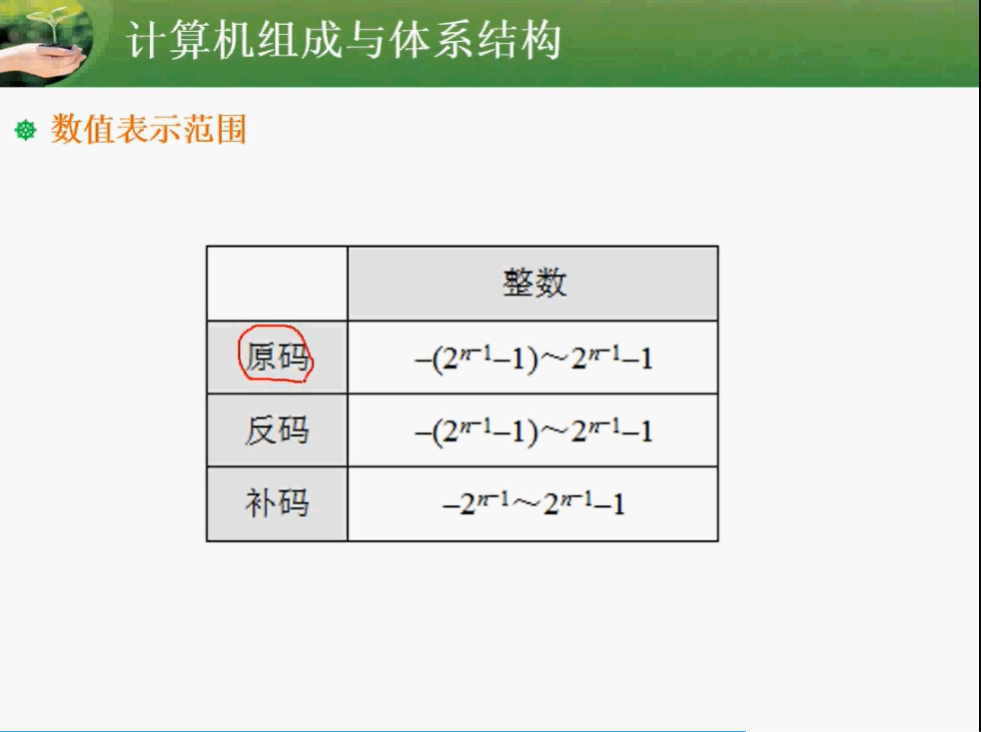

n: 表示数位

浮点数运算

对阶:对低阶

浮点数的表示分为阶和尾数两部分。两个浮点数相加时,需要先对阶,即( 将小阶向大阶对齐,同时将尾数右移n位 )(n为阶差的绝对值)。

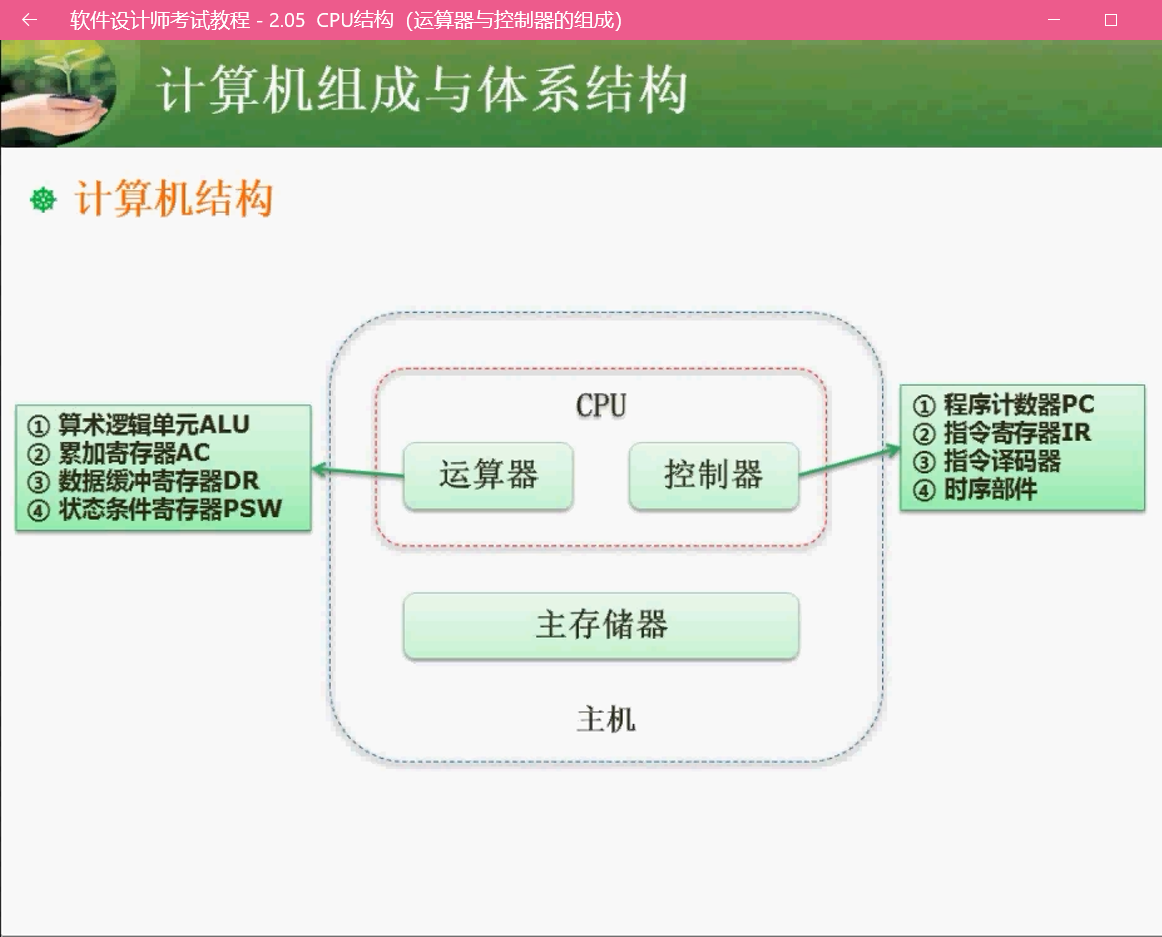

计算机结构

CPU由运算器,控制器,寄存器组等内部总线等部件组成。

运算器是执行部件,用于完成计算机的各种算数和逻辑运算。

控制器决定计算机运行过程的自动化,不仅保证程序的正确执行,还能够处理异常事件。控制器包括指令控制逻辑,时序控制逻辑,总线控制逻辑和中断控制逻辑。

寄存器组可分为专用寄存器和通用寄存器。运算器和控制器中的寄存器是专用寄存器,它们的作用是固定的。通用寄存器可由程序员规定其用途。

多核CPU

Intel的方案称为“双芯”,AMD的方案称为“双核”。

计算机体系结构分类-(Flynn, CISC与RISC)

单指令流单数据流 —- 单片机

多指令流多数据流 —- 主流计算机

RISC — 主流计算机

流水线

流水线的这个部分知识点比较用PPT显得太长,可以看这篇博客。

https://www.cnblogs.com/yandashan666/p/11426482.html (该文章没有流水线的吞吐率计算)

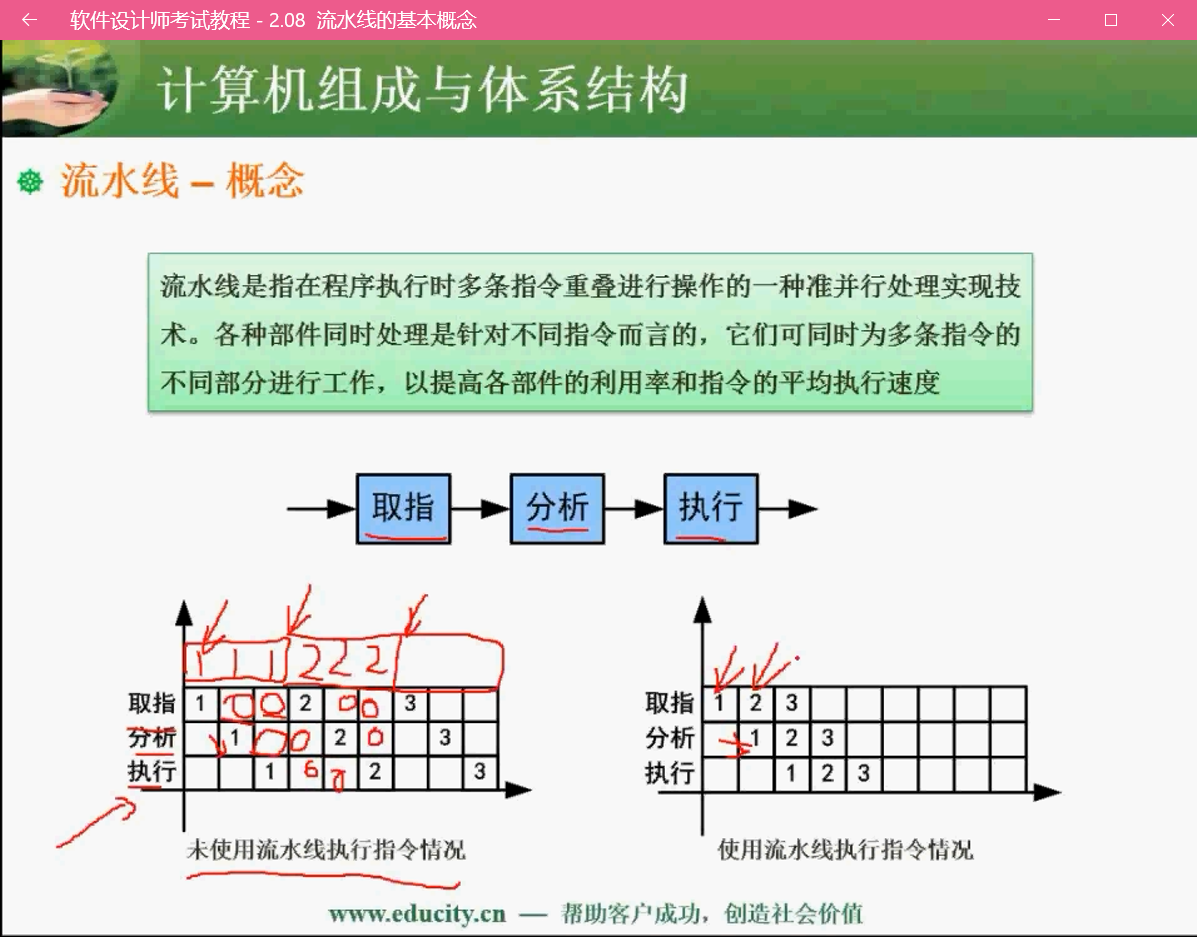

概念

类似工业流水线,如福特公司在开始的时候以班为单位组装汽车,表面看上去时间是连续的,但是实际上组装单台汽车时,不同职能的人不可能同时都在干活,这就造成了时间上的浪费。

流水线计算

首先用理论公式,如果答案里面没有理论公式答案,就用实践公式。

k为一条指令所包含的部分的多少, 例题这里就是3

理论公式一开始的t1+t2+t3+……+tk 指的是第一条指令执行完成所需时间,即建立流水线的时间。第二条指令完成时间是第一条指令完成后的一个流水线周期。第三条指令完成时间是第二条指令完成后的一个流水线周期,以此类推。

实践公式就是在理论公式的基础上,认为每条指令的执行时间为一个流水线周期,即等于 k * △t + (n-1)*△t

流水线周期为指令执行时间最长的一段。这个理解其实把图片中的例题实际情况代入就看出来了。就如同泡茶五分钟,洗茶具三分钟,准备茶叶两分钟,问能喝上茶所需要的时间。

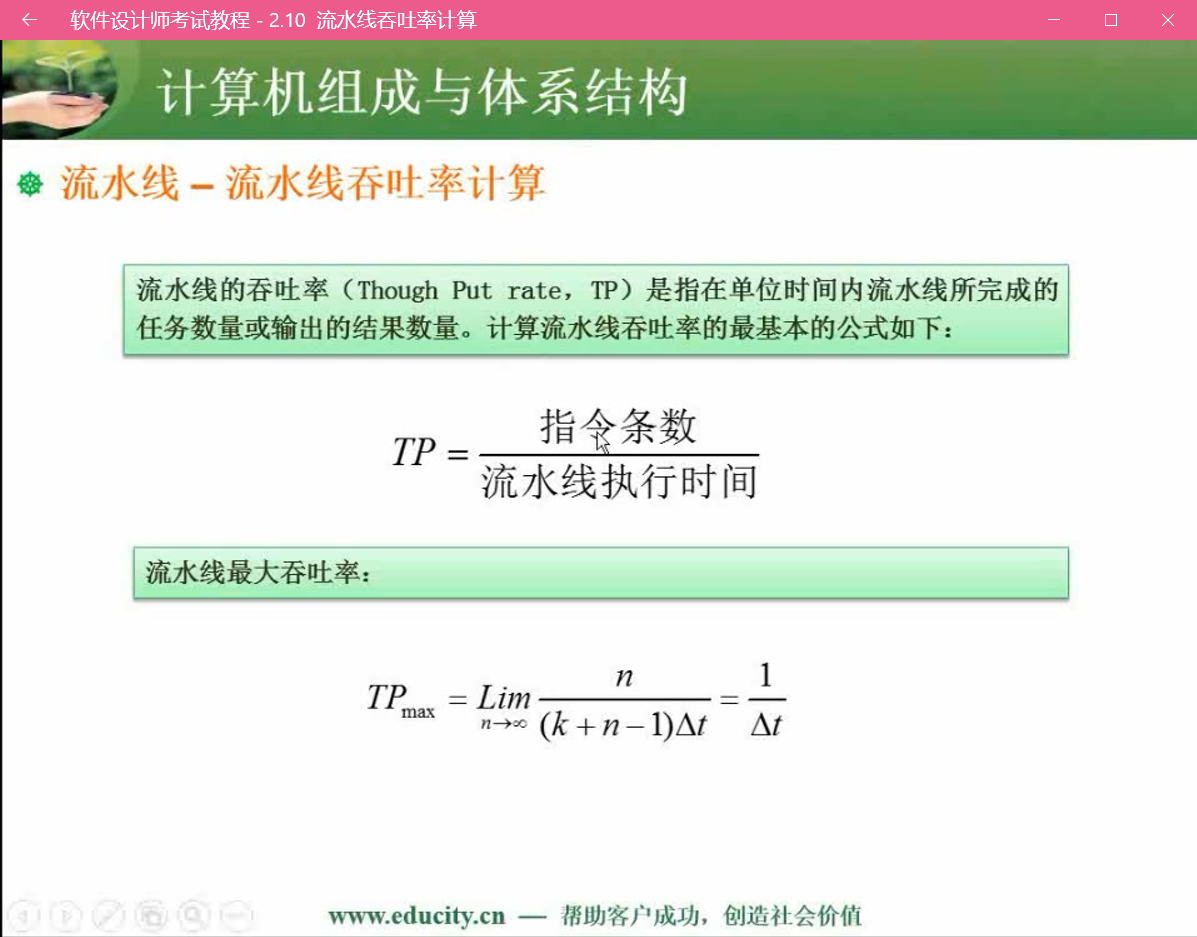

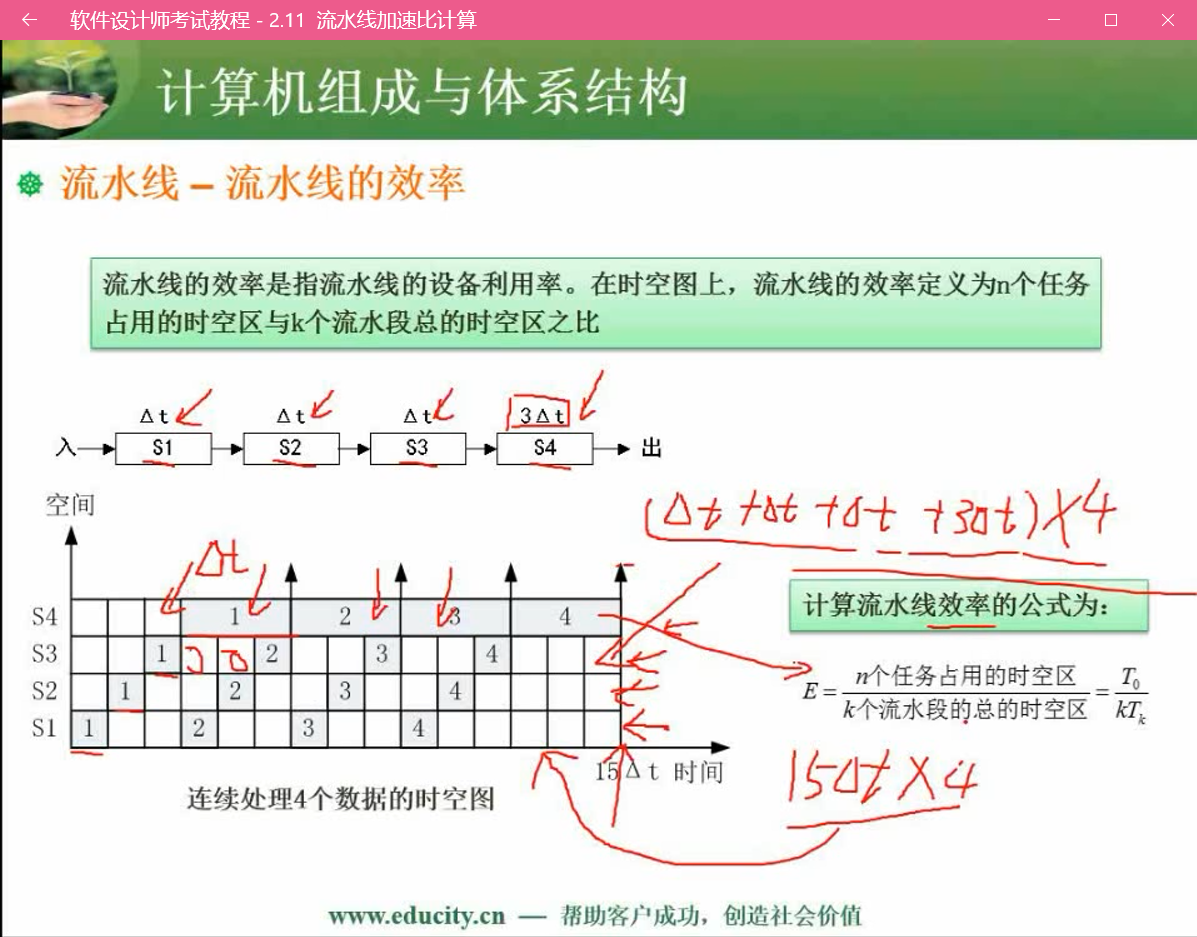

吞吐率

流水线的吞吐率是指单位时间流水线处理的任务数,如果各段流水的操作时间不同,则流水线的吞吐率是(最长流水段操作时间)的倒数。

加速比

S越大,使用流水线的效果越好。 加速比是大于或等于1的。

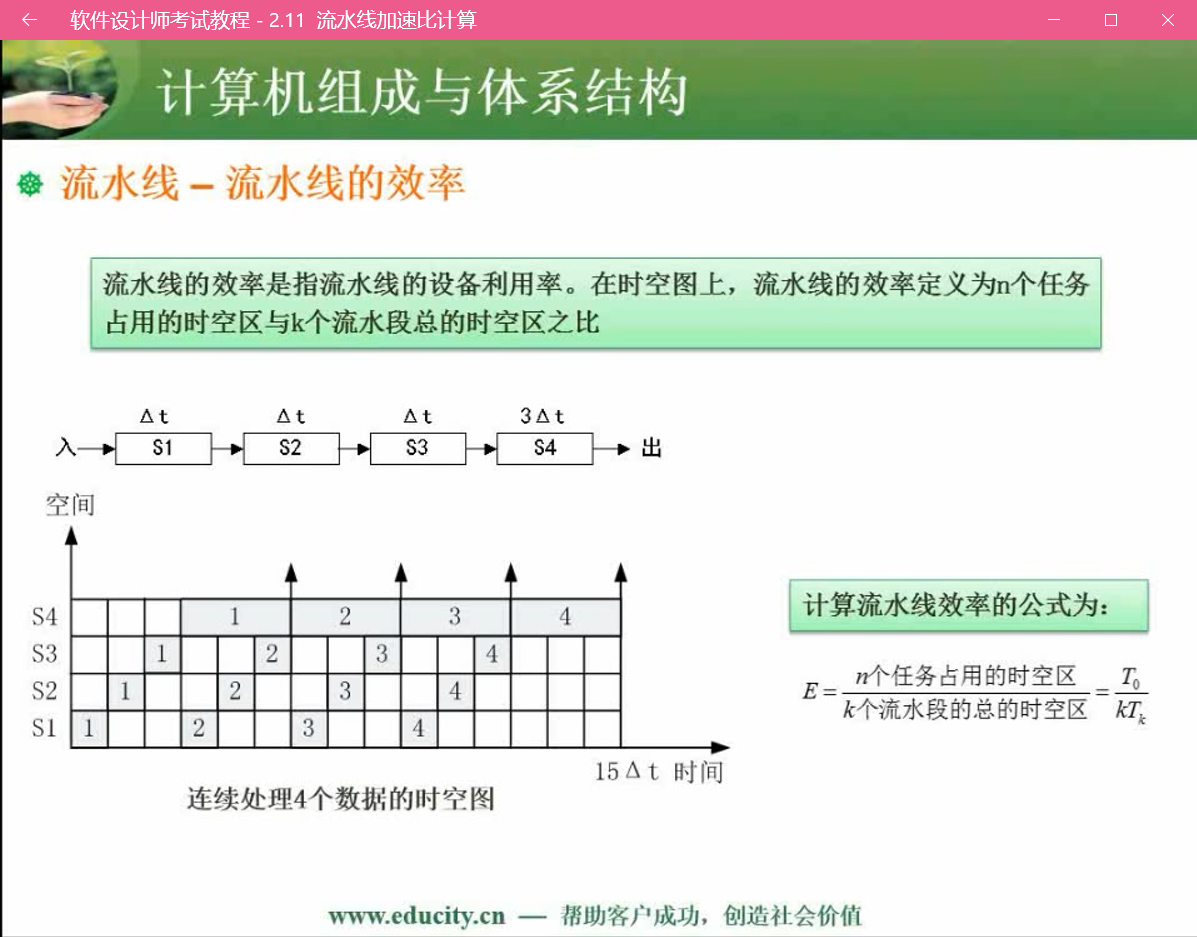

效率

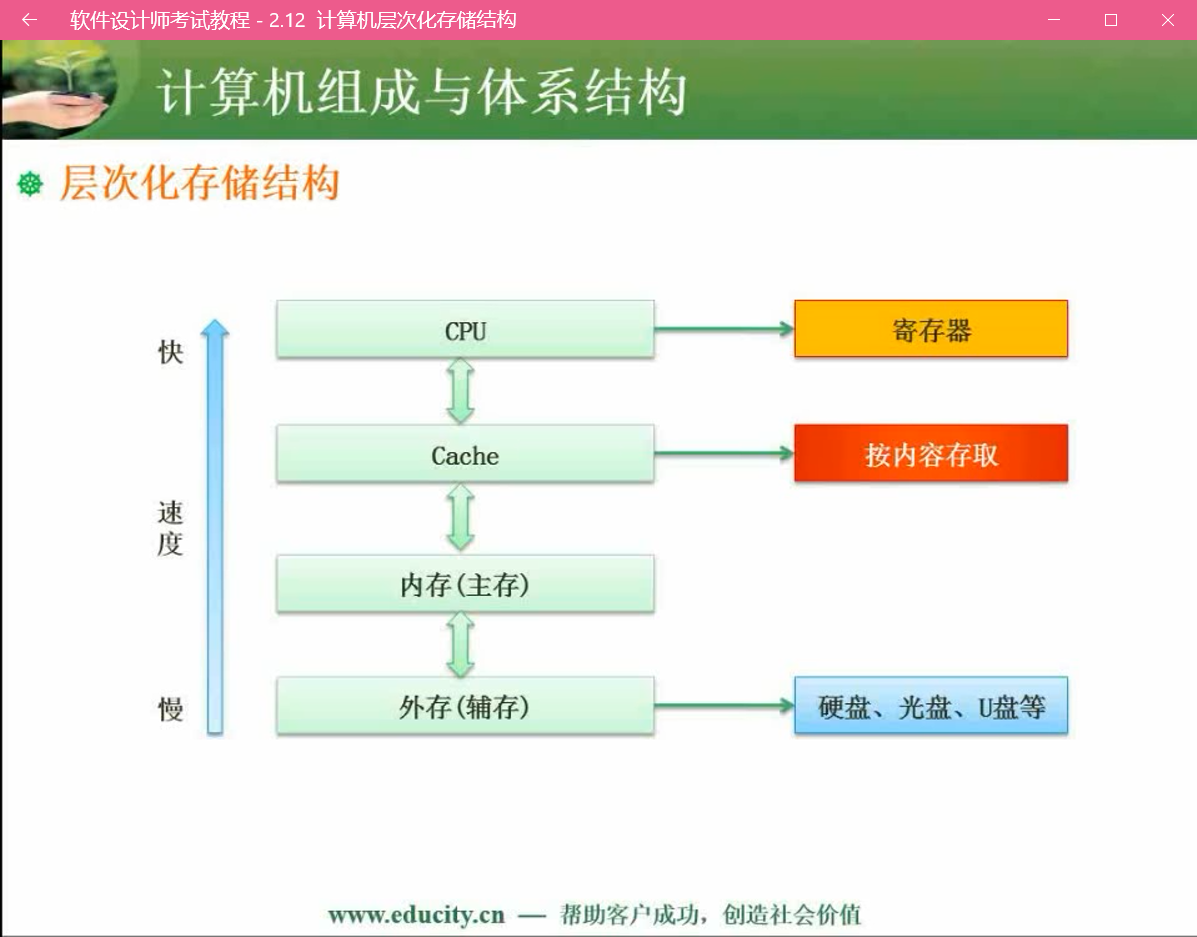

层次化存储结构

存储器结构中寄存器最快,接下来是高速缓存存储器(Cache)

CPU可以直接和内存交换数据,不经过Cache,但是会慢很多。所以加入Cache是一个性价比极高的方案。

Cache有个很显著的特色—按内容存取。 速度和效率会远高于按地址存取的方式。

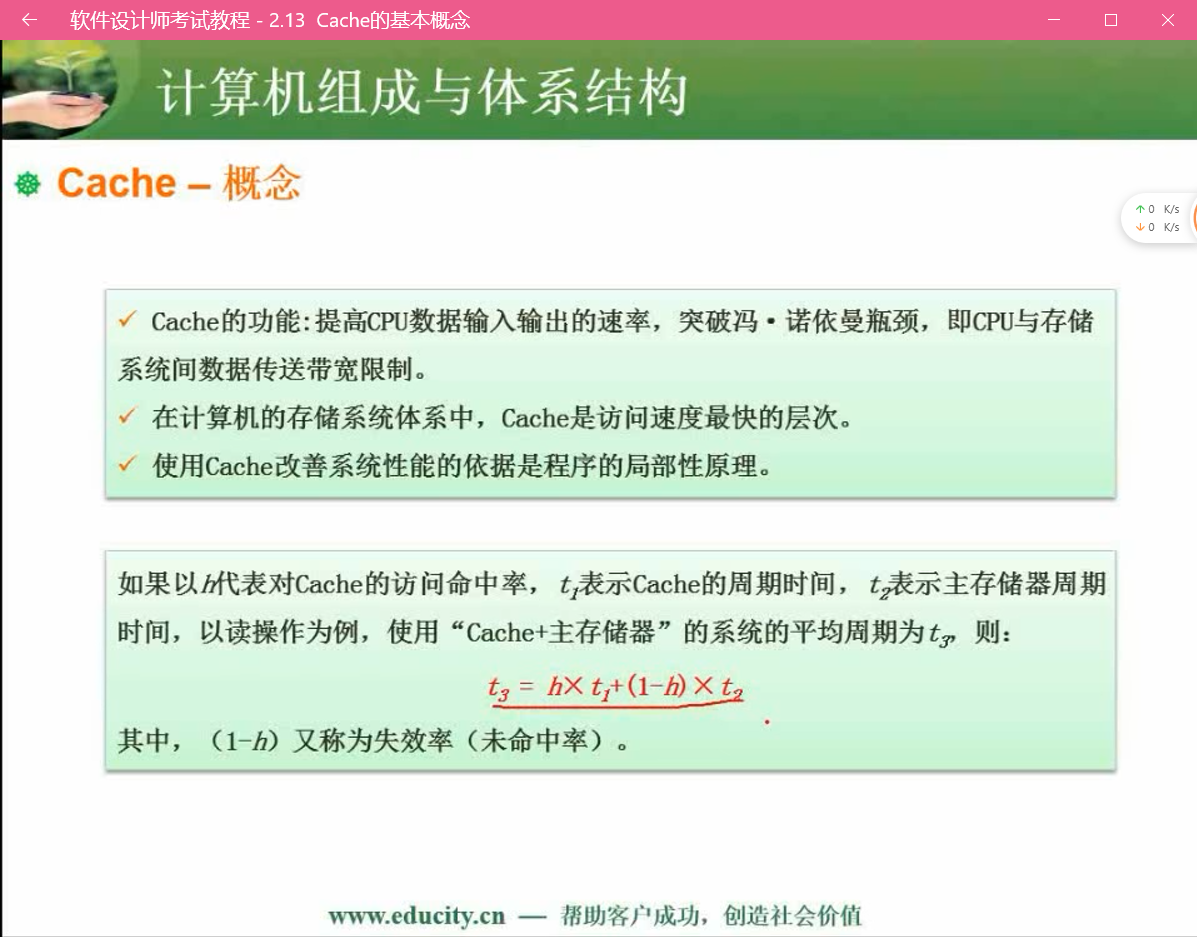

Cache的概念

计算机中访问速度最快的是寄存器,但是没有把它认为是计算机的存储系统。

1秒=1000毫秒

1 毫秒=1000 微秒

1微秒=1000纳秒

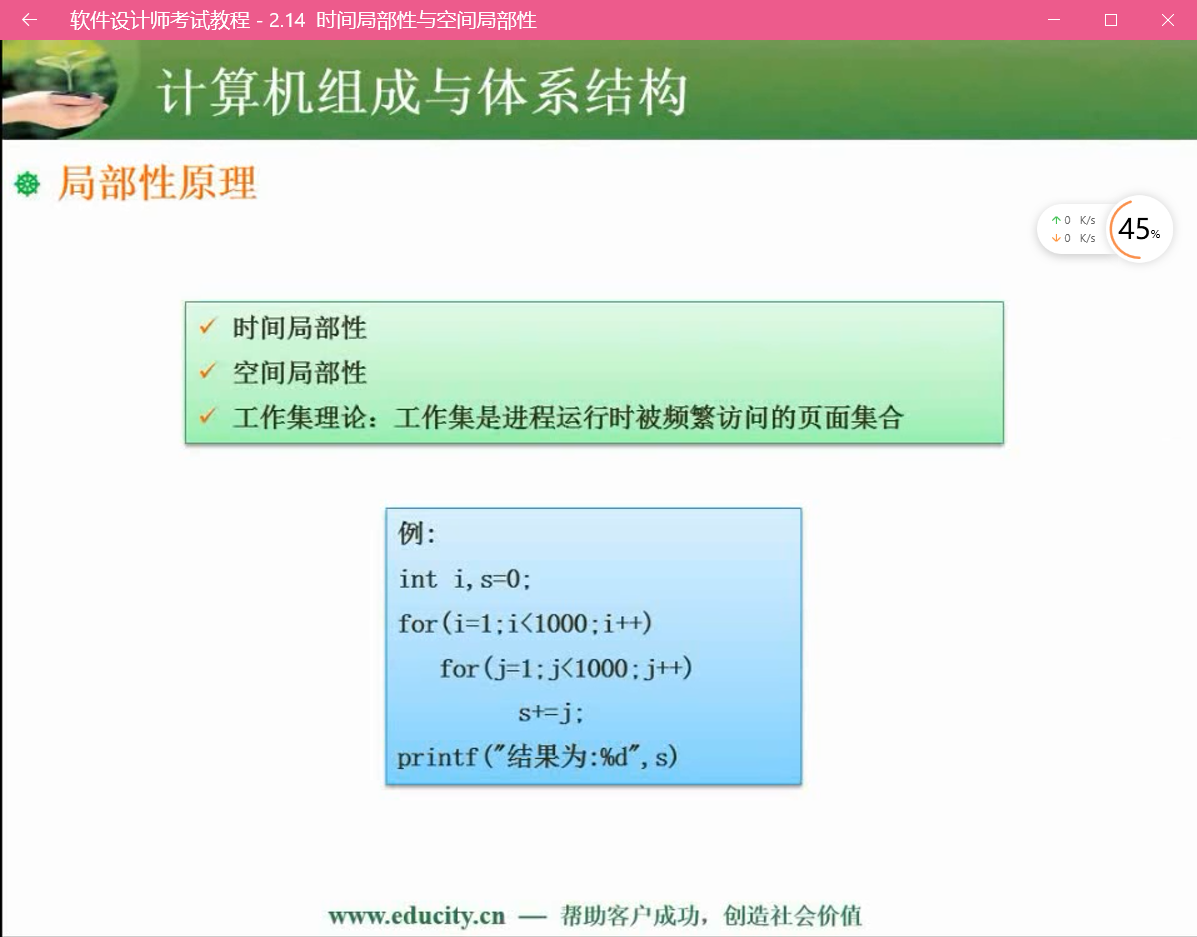

局部性原理

下面转自:

https://www.cnblogs.com/xindoo/p/11303906.html

所以什么是 局部性 ?这是一个常用的计算机术语,是指处理器在访问某些数据时短时间内存在重复访问,某些数据或者位置访问的概率极大,大多数时间只访问_局部_的数据。基于局部性原理,计算机处理器在设计时做了各种优化,比如现代CPU的多级Cache、分支预测…… 有良好局部性的程序比局部性差的程序运行得更快。虽然局部性一词源于计算机设计,但在当今分布式系统、互联网技术里也不乏局部性,比如像用redis这种memcache来减轻后端的压力,CDN做素材分发减少带宽占用率……

时间局部性(Temporal locality):

如果某个信息这次被访问,那它有可能在不久的未来被多次访问。时间局部性是空间局部性访问地址一样时的一种特殊情况。这种情况下,可以把常用的数据加cache来优化访存。

空间局部性(Spatial locality):

如果某个位置的信息被访问,那和它相邻的信息也很有可能被访问到。 这个也很好理解,我们大部分情况下代码都是顺序执行,数据也是顺序访问的。

局部性的实际应用

从最快的L1 Cache到最慢的HDD,其两者的访存时间差距达到了6个数量级,即便是和内存比较,也有几百倍的差距。举个例子,如果CPU在运算是直接从内存中读取指令和数据,执行一条指令0.3ns,然后从内存读下一条指令,等120ns,这样CPU 99%计算时间都会被浪费掉。但就是因为有局部性的存在,每一层都只有少部分数据会被频繁访问,我们可以把这部分数据从底层存储挪到高层存储,可以降低大部分的数据读取时间。

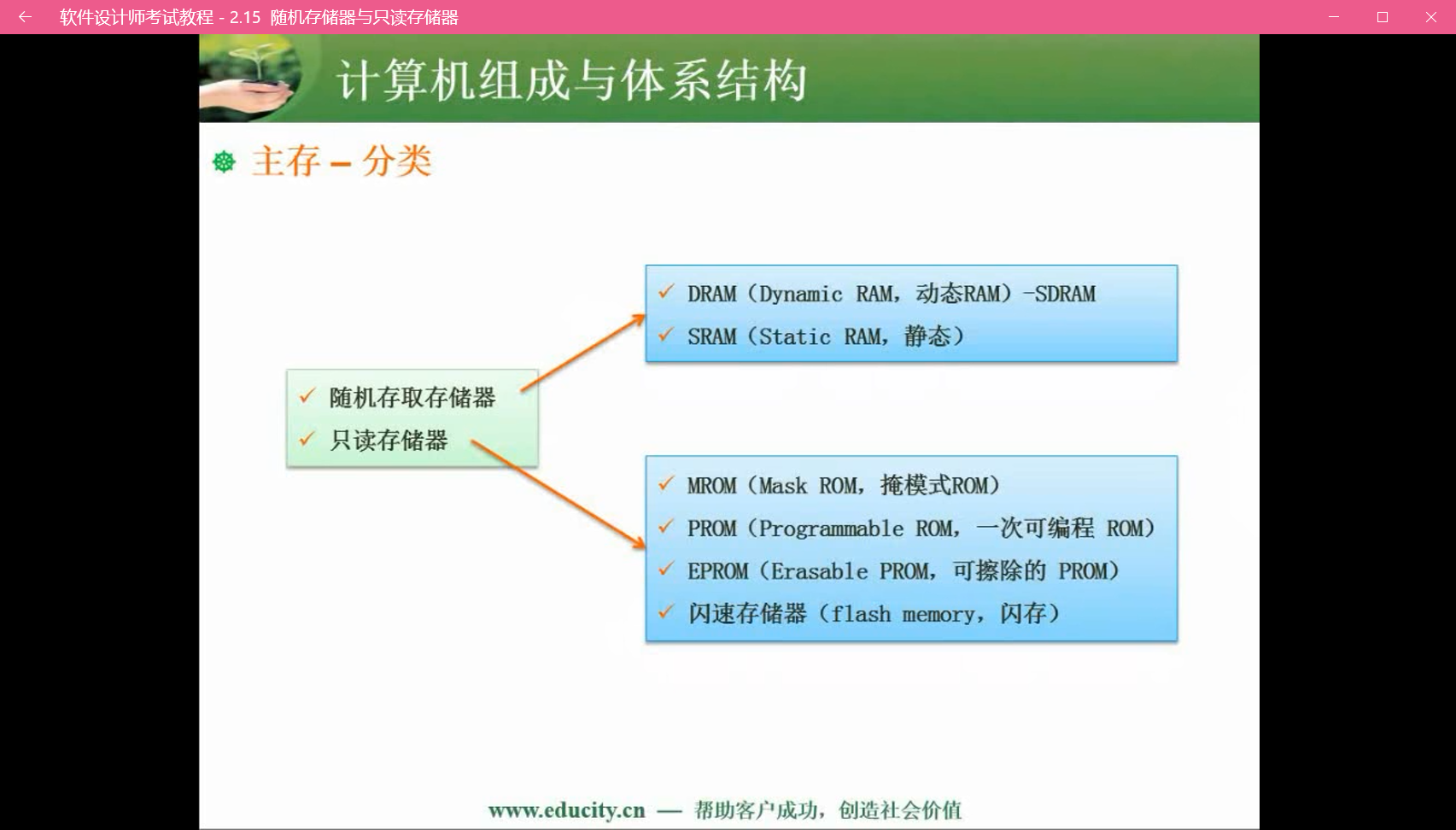

主存的分类

随机存取存储器和只读存储器

随机存取存储器,如内存,特点是一旦断电,里面的数据无法保存下来

只读存储器,如bios的芯片,特点是断电后信息也可以保存下来

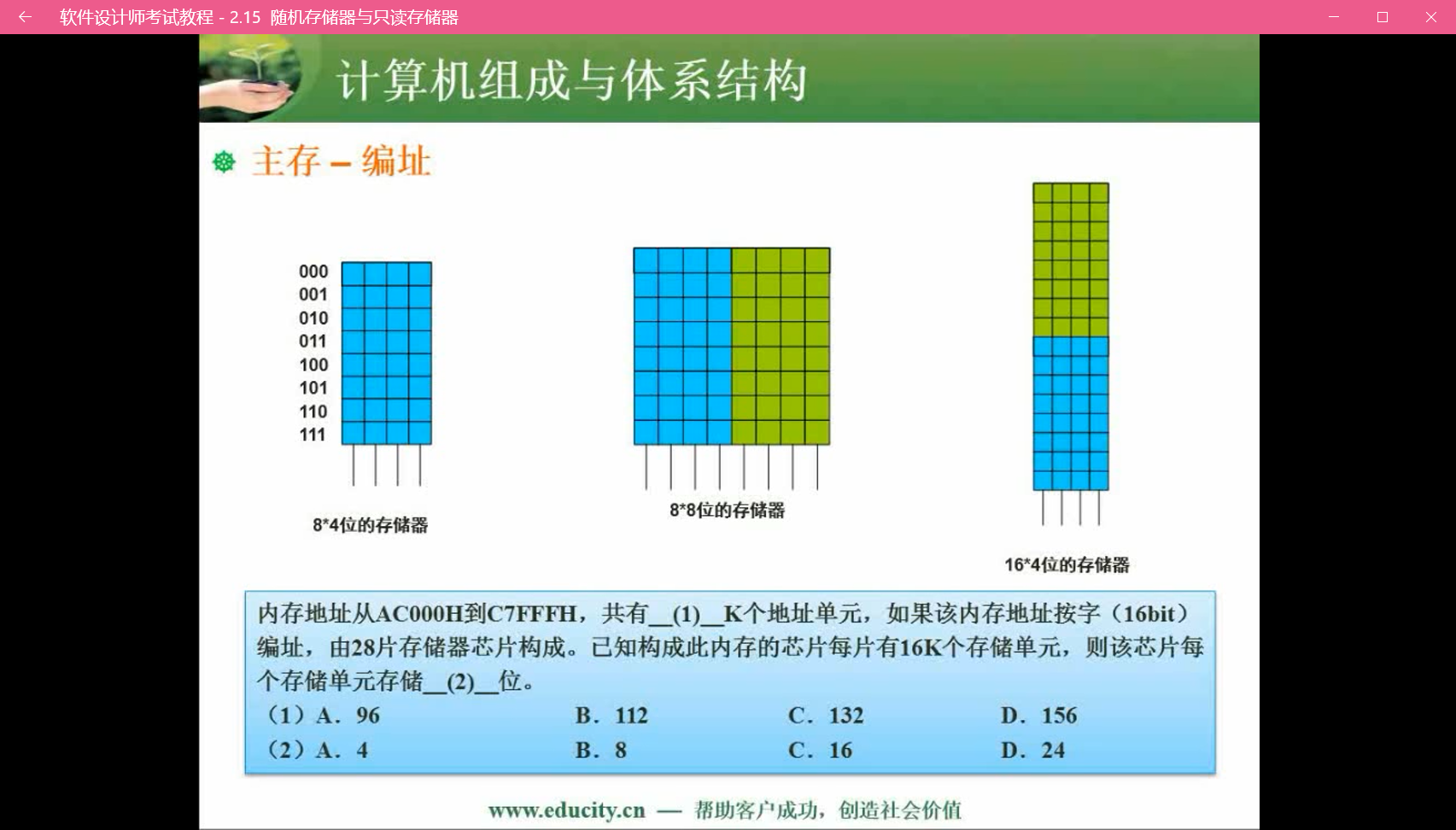

主存的编址

考点

解答:

1 | 1. C7FFFH + 1 - AC000H = C8000H - AC000H = 1C000H |

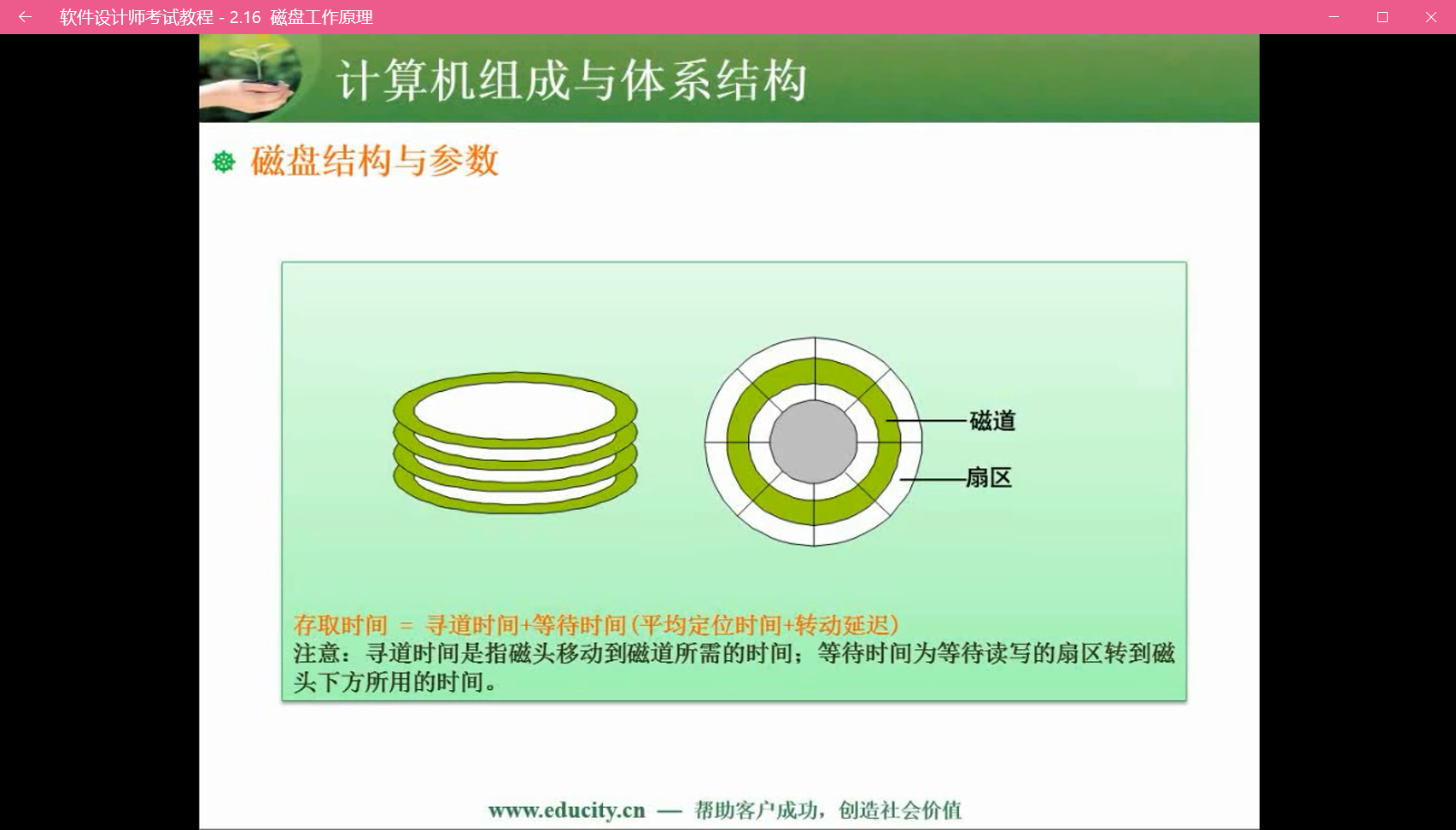

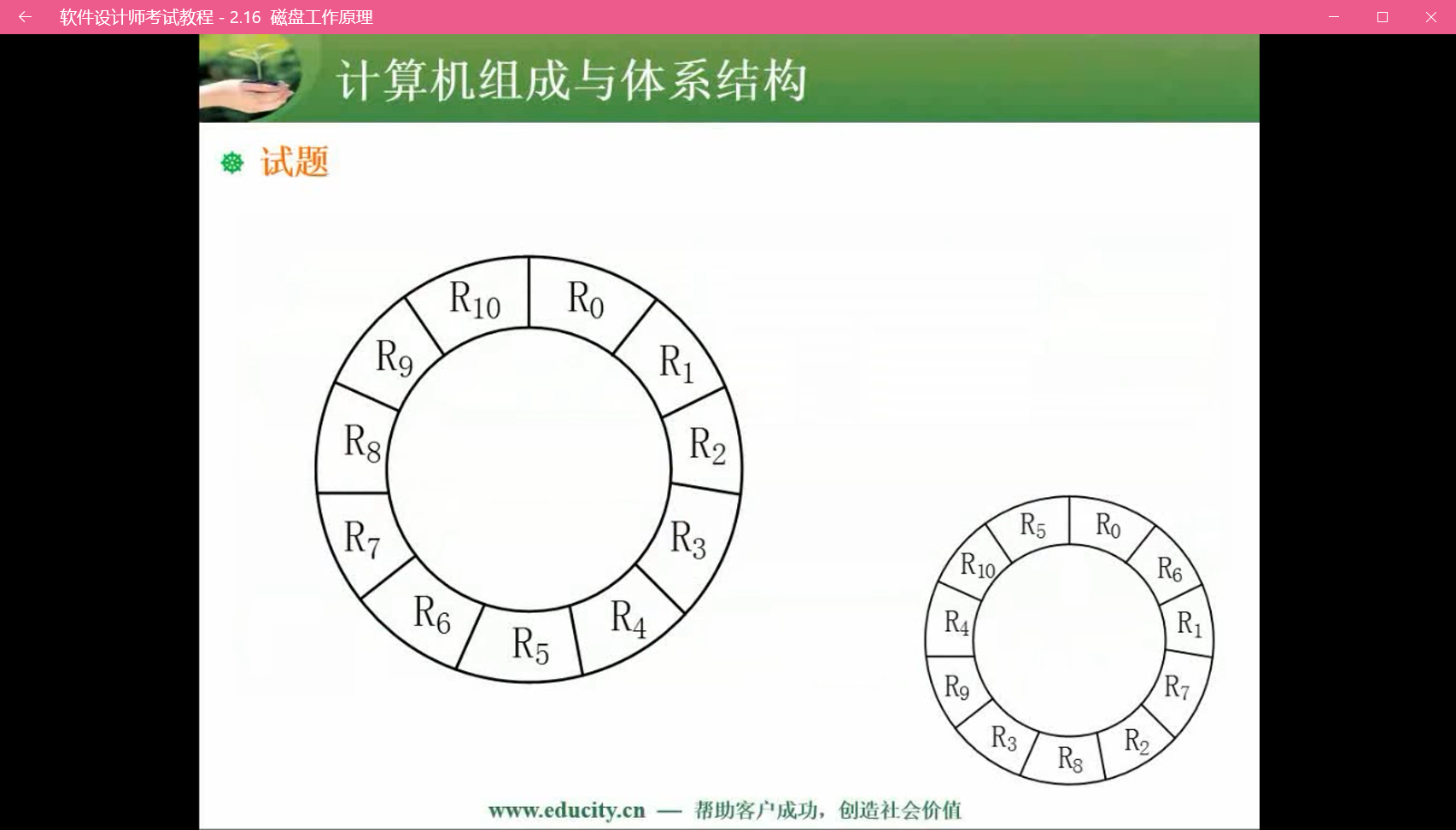

磁盘结构与参数

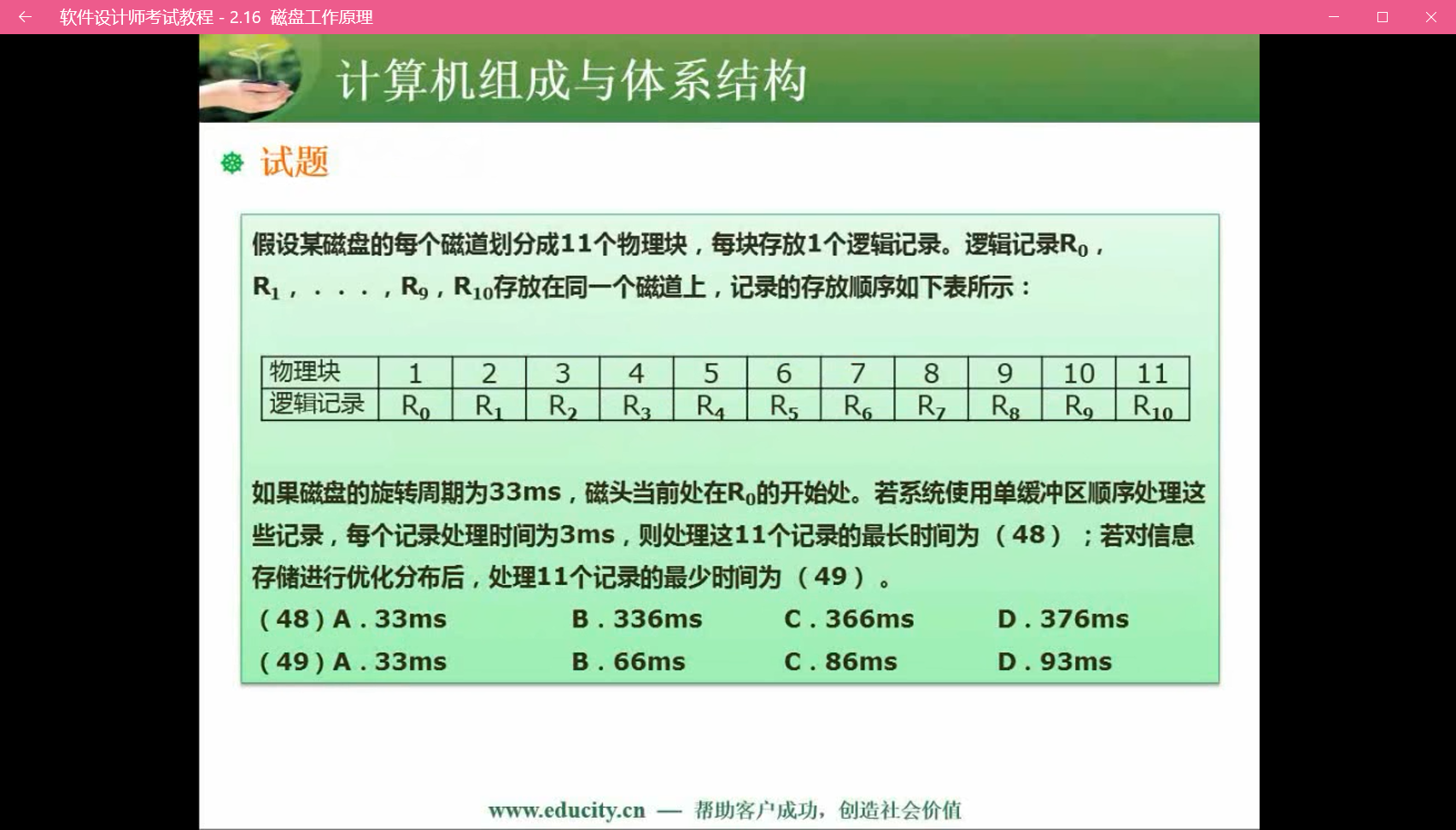

解答:

1 | 磁盘磁道形象图如上图1。首先,需要做到单缓冲区处理记录的时候无法增加新记录,需要处理完成后才可以添加记录,所以R0进去了,R1无法紧随之。 |

总线

系统可靠性分析

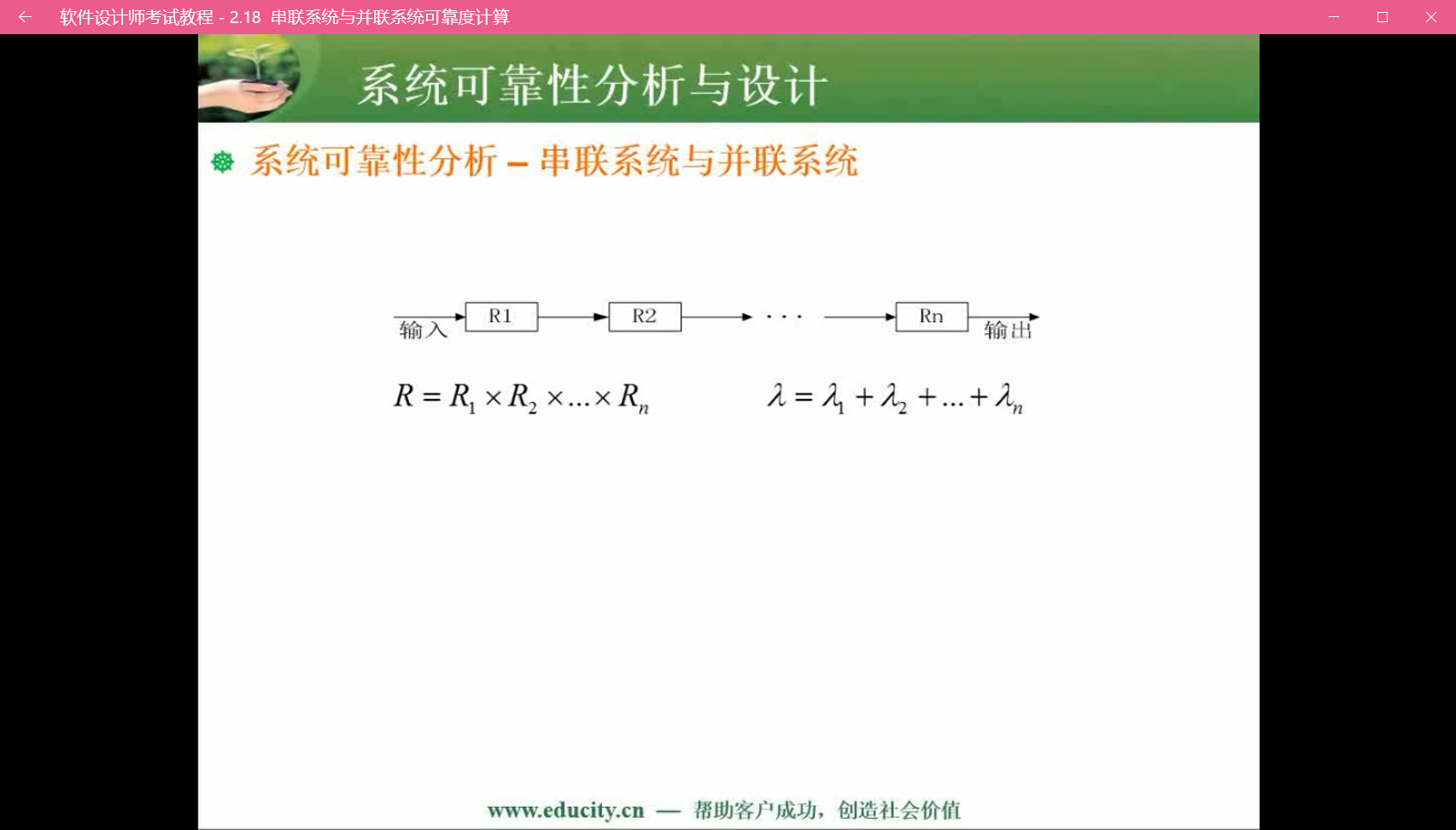

串联系统与并联系统

串联系统:可靠性 R = R1 * R2 * R3 * …… * Rn

失效率 γ = γ1 + γ2 + γ3 + …… + γn (计算出来的结果是近似的)

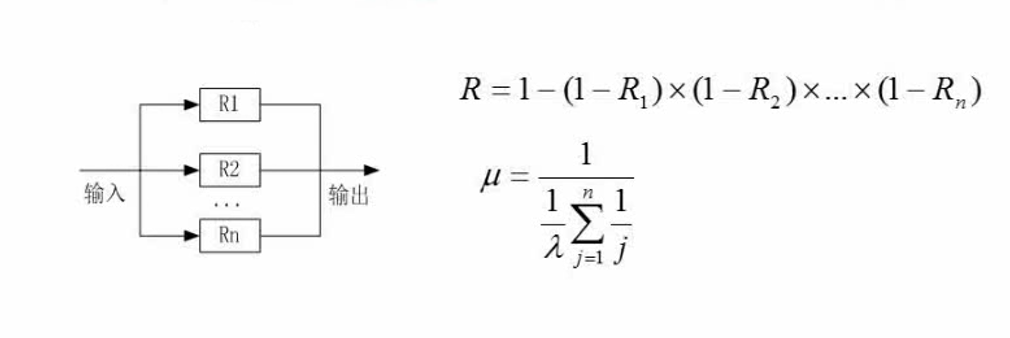

并联系统:可靠性 R = 1 - (1 - R1) * (1 - R2) * …… * (1 - Rn)

即:所有子系统失效的时候才失效

失效率 γ = (1 - R1) * (1 - R2) * …… * (1 - Rn) = 1 - R (上图公式比较复杂,可以通过这种方式得出)

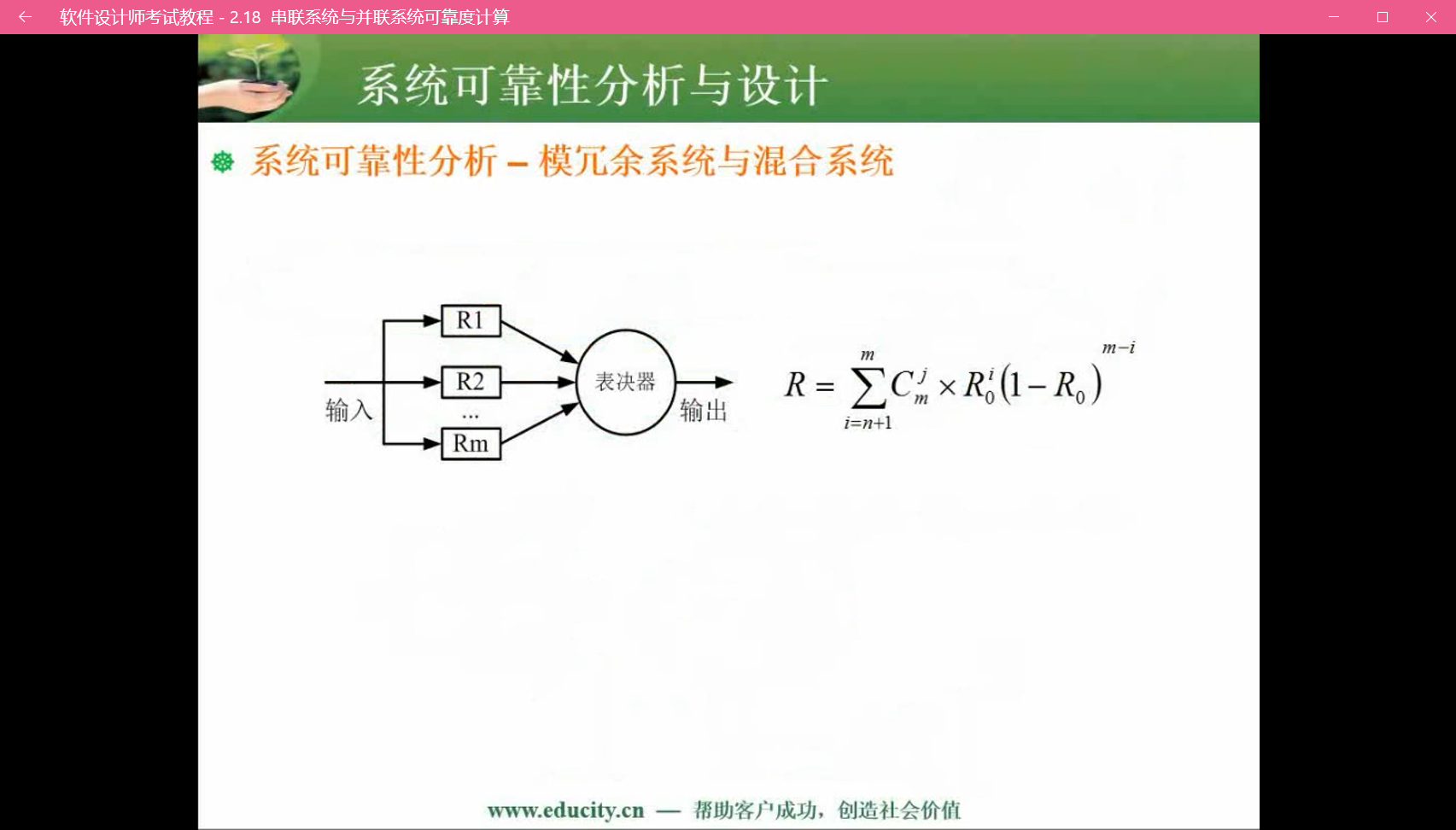

模冗余系统与混合系统

R1,R2,Rm子系统都对输入进行处理,再由表决器决定采用哪个的结果,如少数服从多数原理

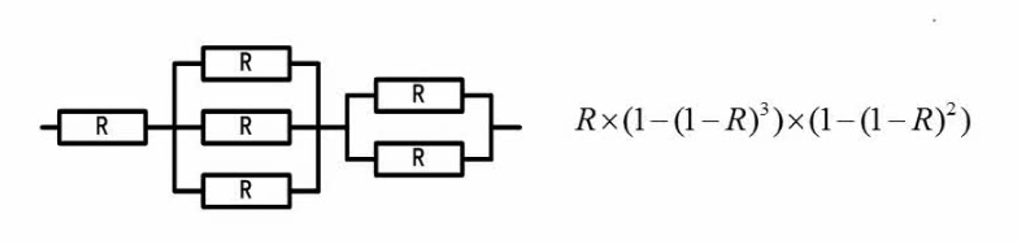

考试比较常遇到的题型,这里总体来看就是一个串联系统,串联系统里面的并联看成整体即可

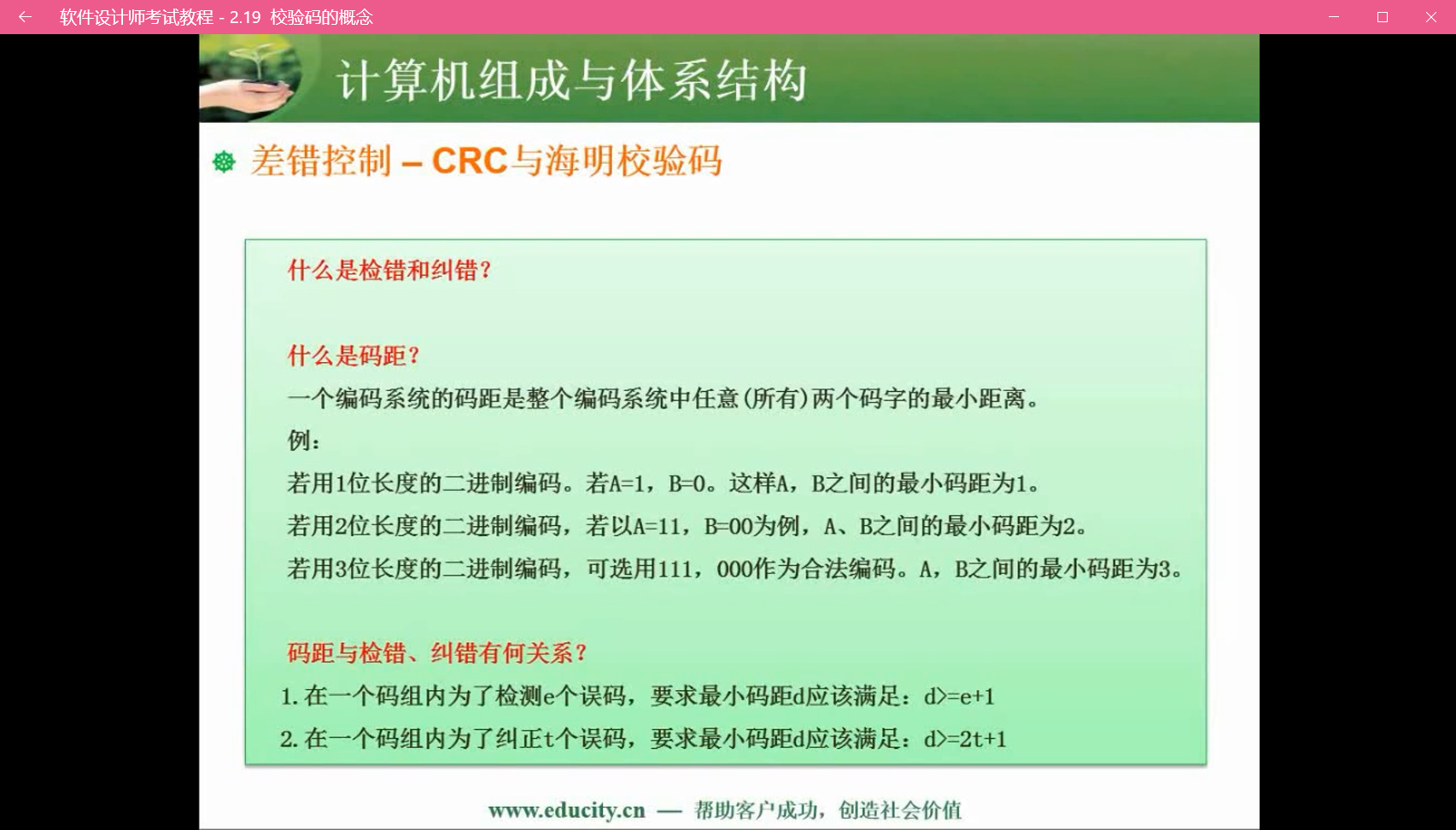

差错控制

这里考虑的是信息传递的过程中最多产生一个误码

校验码

https://baijiahao.baidu.com/s?id=1594263251060755624&wfr=spider&for=pc

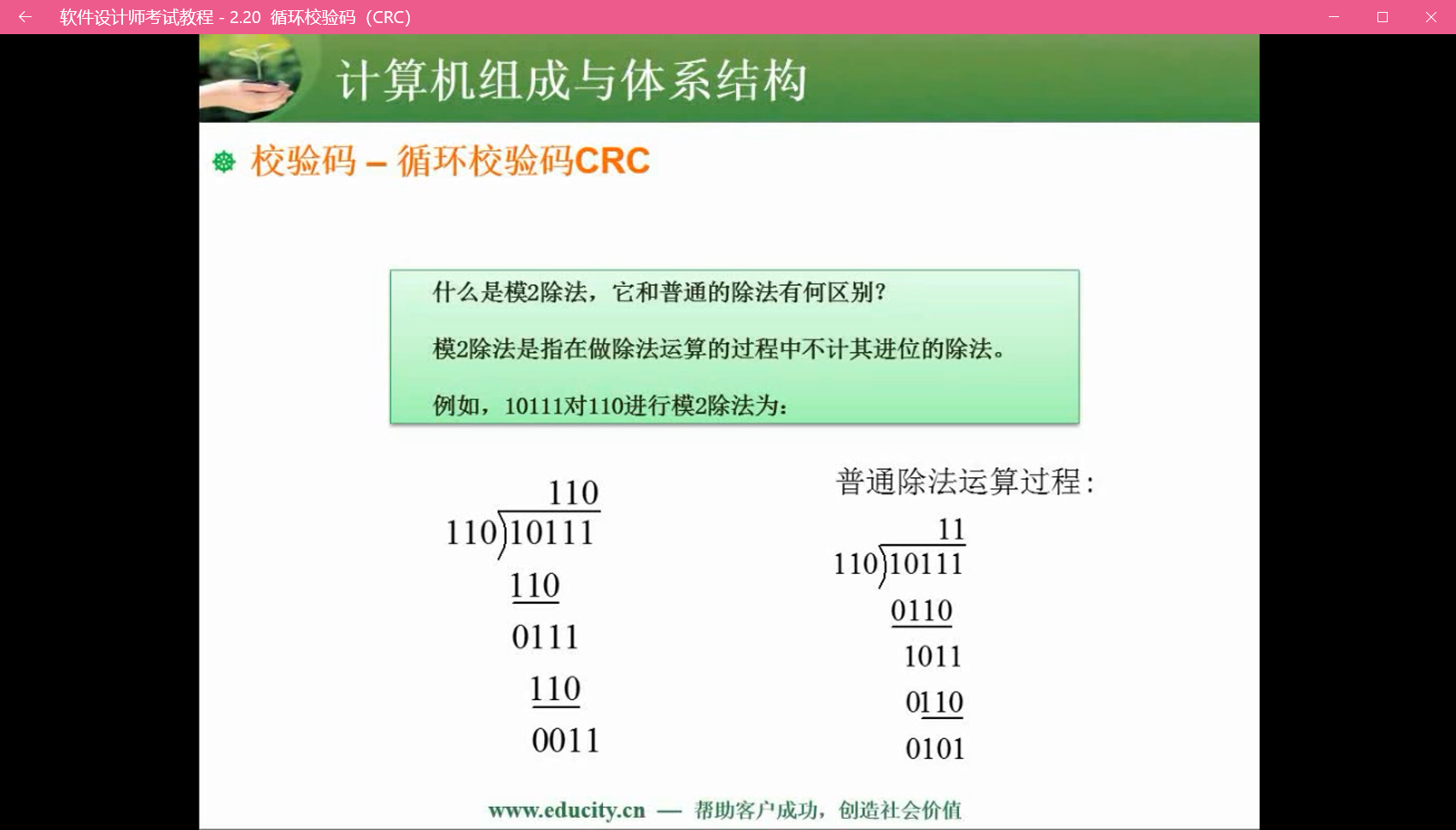

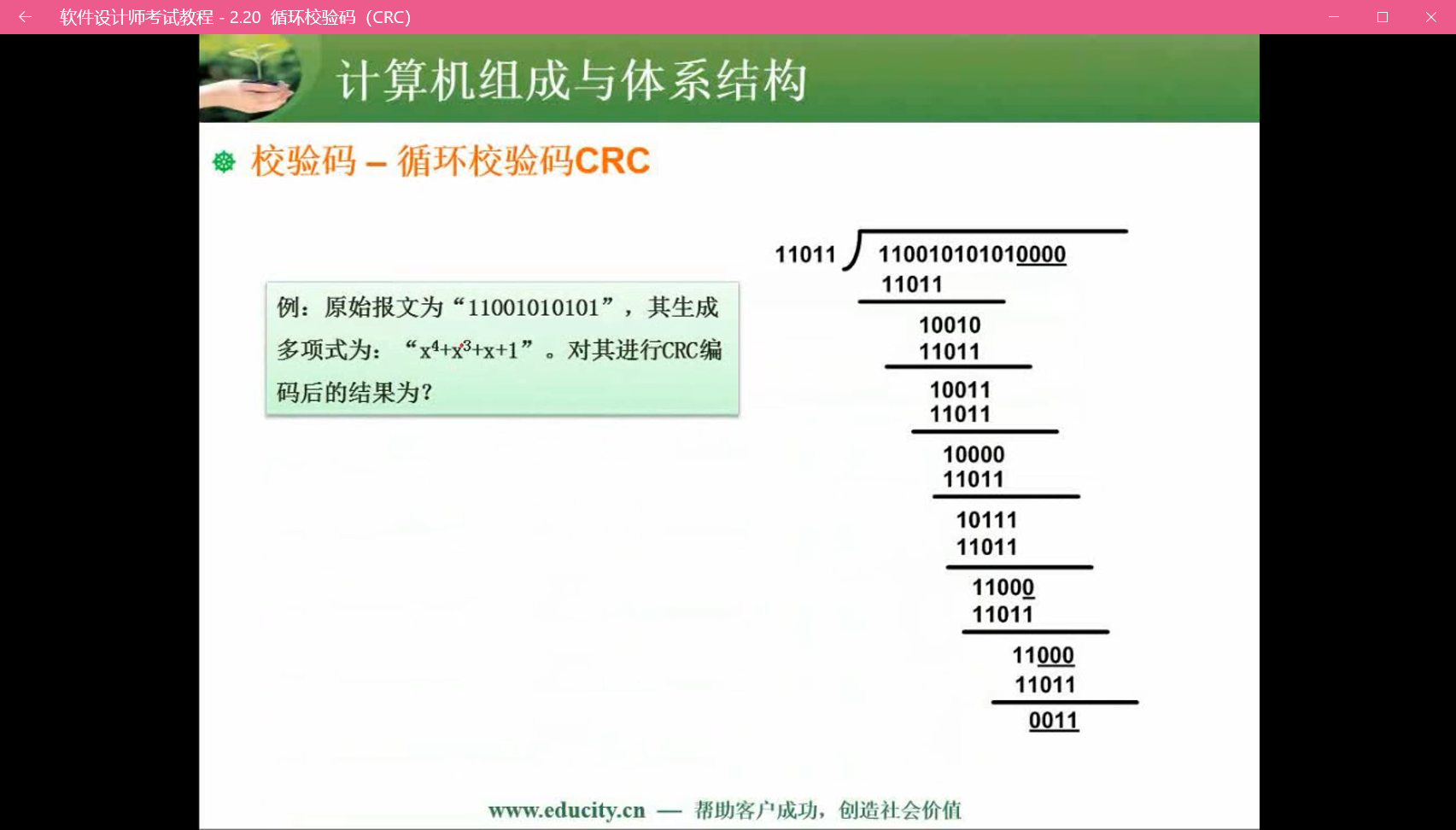

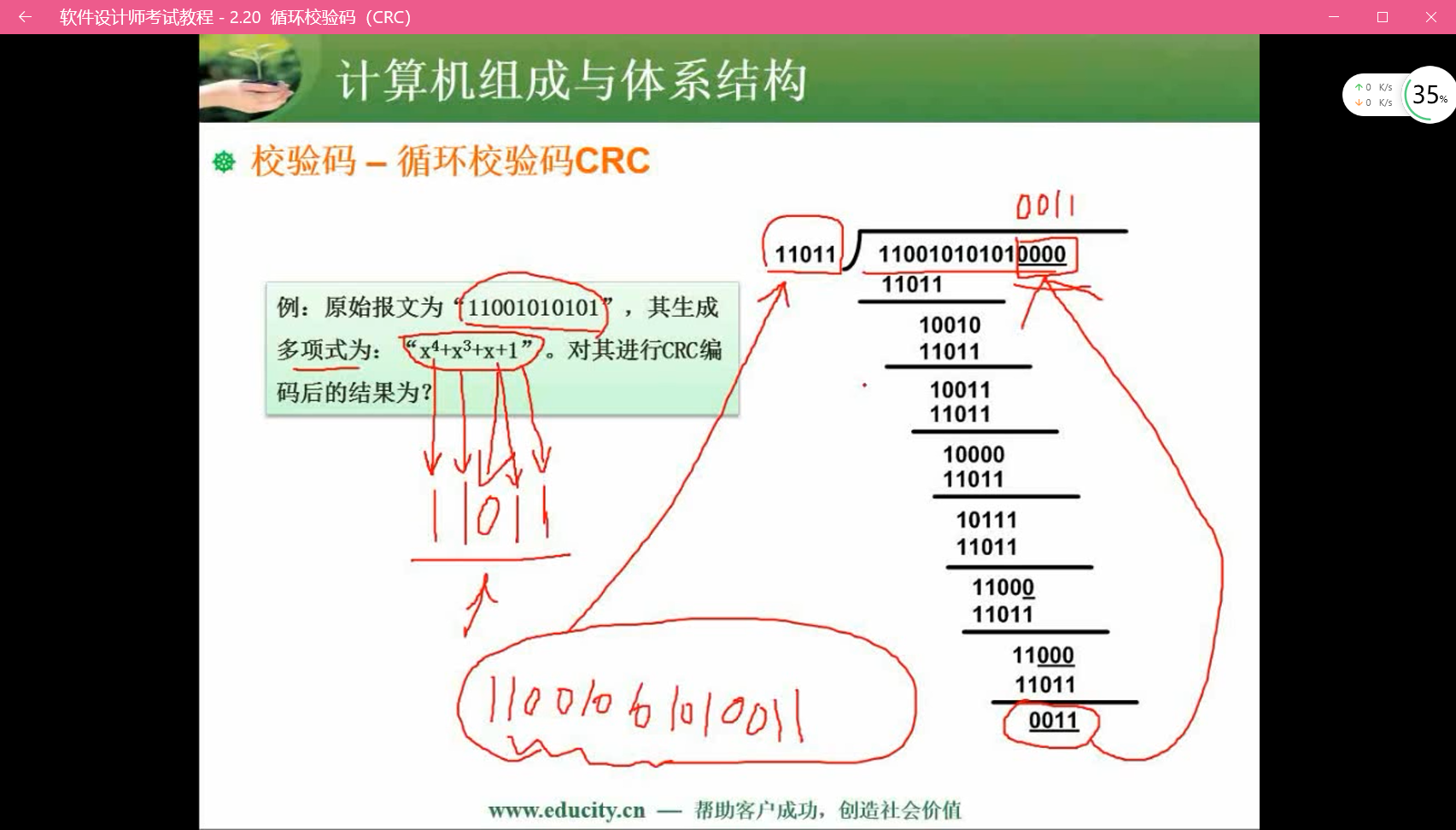

循环校验码和CRC

https://www.cnblogs.com/liushui-sky/p/9962123.html

按位异或

生成多项式x^4+x^3+x+1转成二进制形式(把x看成是2)即是11011,用原始报文补余数位(这里11011的余数位为长度5-1=4),然后进行上面的模2除法,得出的余数替换掉原来的余数位得到的就是CRC编码

得到的CRC编码对11011进行模2除法得到余数为0,则可以判断CRC编码正确。

海明校验码(难点,考点)

1 | r: 校验位 |

海明校验码除了可以检错还可以纠错

海明不等式:校验码个数为K,2的K次方个校验信息,1个校验信息用来指出“没有错误”,满足m+k+1<=2k(m为二进制数据长度)。所以32位的数据位,需要

k位校验码, 有 32 + k + 1 <= 2k => k = 6。

本文链接: http://www.ionluo.cn/blog/posts/14ca2885.html

版权声明: 本作品采用 知识共享署名-非商业性使用-相同方式共享 4.0 国际许可协议 进行许可。转载请注明出处!